# AN14284

# **Timing Parameter Tuning for FlexIO Emulated Interface**

Rev. 1 — 12 April 2024

**Application note**

#### **Document information**

| Information | Content                                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------------------|

| Keywords    | AN14284, FlexIO, SPI                                                                                             |

| Abstract    | This application note describes how to use additional timers to tune the setup time in SPI master in RT1170-EVK. |

#### **Timing Parameter Tuning for FlexIO Emulated Interface**

#### 1 Introduction

FlexIO is an on-chip peripheral available on Kinetis, S32K, RT, and MCX microcontroller families. It is highly configurable and capable of emulating a wide range of communication protocols, such as UART, I<sup>2</sup>C, SPI, I<sup>2</sup>S, and LIN and others more like J1850, I3C, Manchester.<sup>1</sup>

The standalone peripheral module FlexIO is used as an additional peripheral module of the microcontroller and is not a replacement of any communication peripheral.

The key feature of FlexIO is its flexibility, which enables users to customize even timing parameters.

This application note describes how to use additional timers to tune the setup time in SPI master in RT1170-EVK.

#### 2 Emulation of SPI master

#### 2.1 Overview

To emulate SPI master in FlexIO, these resources are used:

- Two shifters: One is a transmitter and the other is a receiver.

- Two timers: One is used for the chip select generation, and the other is used for clock generation to control two shifters.

- Four pins: CS, SCK, MOSI, and MISO.

#### 2.2 Receiving error at a high baud rate

The driver to emulate SPI master is typically included in the MCUXpresso SDK. Here is the result when evkmimxrt1170 flexio spi edma lpspi transfer master cm7 is running at 20 MHz.

SPI master receives one-bit shifted data and error occurs somehow as shown below.

```

FLEXIO Master edma - LPSPI Slave edma example start.

This example use one flexio spi as master and one lpspi instance as slave on one board.

Master uses edma and slave uses edma way.

Please make sure you make the correct line connection. Basically, the connection is:

FLEXIO_SPI_master -- LPSPI_slave

CLK

__

CLK

PCS

PCS

SOUT

--

SIN

__

SIN

SOUT

This is LPSPI slave call back.

Master receives:

FF

FE

모모

FE

FD

FD

FC

FC

FR

FR

FA

FA

F9

F9

F۵

F۵

F7

F7

F6

F5

F5

F4

F3

F3

F2

F1

F0

F0

Slave transmits:

FD

F8

FE

FC

FB

FA

F9

F7

F6

F4

F3

F2

F1

F0

EΕ

ED

EC

EΒ

EΑ

E9

E8

E7

Ε6

E5

E4

E3

E2

E1

ΕO

Error occurred in FLEXIO SPI master <-> LPSPI slave transfer!

End of example.

```

AN14284

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

<sup>1</sup> Using FlexIO to emulate Quad SPI master (document <u>AN14175</u>)

Using FlexIO to emulate communications and timing peripherals (document <u>AN12174</u>)

#### **Timing Parameter Tuning for FlexIO Emulated Interface**

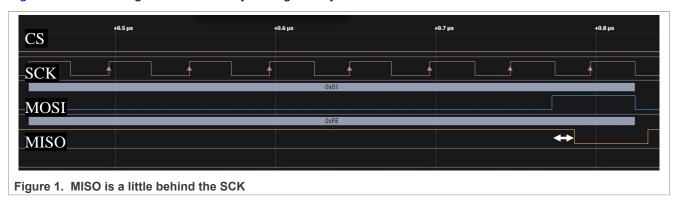

Figure 1 shows the signals measured by the logic analyzer.

MISO is a little bit behind the SCK because the slave device is driven by the master device, but MISO is sampled by the positive edge of SCK. That results in a one-bit shifted data.

This is what is called setup time. Latency depends on how fast the connected slave device is.

## 3 Setup time tuning by delayed clock

#### 3.1 What is a delayed clock

In naive implementation, the receiver is shifted by the positive edge of SCK, which results in a one-bit shift when MOSI is a little behind the SCK. By using the internal delayed clock for the receiver, the master receives correct data even if MOSI is behind the SCK.

#### 3.2 Configuring the shifters and timers

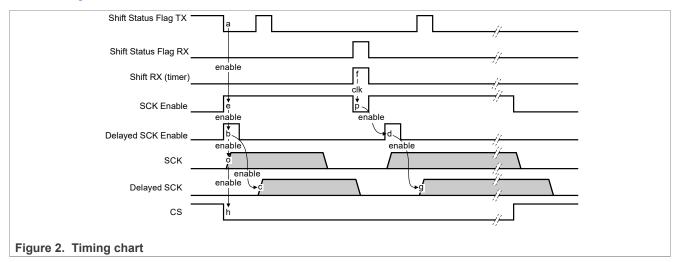

Additional four timers are needed to realize the delayed clock. While the transmit shifter is controlled by SCK as usual, the receive shifter is controlled by Delayed SCK. The output of each timer must follow the timing chart, as shown in <u>Figure 2</u>.

- Shifter RX is added to convert Shifter Status Flag (SSF) into timer output. It is used for SCK Enable.

- SCK is enabled when SCK Enabled is asserted. SCK Enable is asserted when SSF TX is low and SSF RX falls.

AN14284

#### Timing Parameter Tuning for FlexIO Emulated Interface

Delayed SCK is enabled when Delayed SCK Enable is asserted. Delayed SCK Enable counts how much Delayed SCK should be delayed. One unit is one FlexIO cycle. In the demo, Delayed SCK is configured to count two cycles, but it is customizable.

Concretely, timers are configured as follows.

Table 1. Timer configuration

| Timer | Name                     | Trigger select        | Pin select                | Enable condition | Disable condition | Decrement source |

|-------|--------------------------|-----------------------|---------------------------|------------------|-------------------|------------------|

| 0     | Shifter RX               | SSF RX                | Output<br>(ShifterRxPin)  | Trigger rising   | Timer compare     | Trigger          |

| 1     | SCK<br>Enable            | SSF TX                | Input<br>(ShifterRxPin)   | Trigger low      | Timer compare     | Pin              |

| 2     | Delayed<br>SCK<br>Enable | SCK Enable            | Not used                  | Trigger rising   | Timer compare     | FlexIO clock     |

| 3     | SCK                      | SCK Enable            | Output<br>(SCKPin)        | Trigger rising   | Timer compare     | FlexIO clock     |

| 4     | Delayed<br>SCK           | Delayed SCK<br>Enable | Output<br>(DelayedSCKPin) | Trigger rising   | Timer compare     | FlexIO clock     |

| 5     | cs                       | SCK Enable            | Output<br>(CSnPin)        | Trigger rising   | Timer compare     | trigger          |

#### 3.3 Running the demo

To make the example work, connections are as shown in Table 2.

Table 2. Pin connection

| Signal                   | Slave  | Master |

|--------------------------|--------|--------|

| MOSI                     | J10-10 | J26-6  |

| MISO                     | J10-8  | J26-4  |

| SCK                      | J10-12 | J26-2  |

| Delayed SCK (Test point) | _      | J26-10 |

| CS                       | J10-6  | J26-8  |

- 1. Remove  $0\Omega$  resistor to R200,R406,R408, and R404.

- 2. Connect a mini USB cable between the PC host and the OpenSDA USB port on the board.

- 3. Open a serial terminal on the computer for OpenSDA serial device with these settings:

- 115200 baud rate

- · 8 data bits

- · No parity

- · One stop bit

- No flow control

- 4. Download the program to the target board.

- 5. Either press the reset button on your board or launch the debugger in your IDE to begin running the demo.

You can see the following message in the terminal if the example runs successfully.

AN14284

### Timing Parameter Tuning for FlexIO Emulated Interface

```

FLEXIO Master edma - LPSPI Slave edma example start.

This example use one flexio spi as master and one lpspi instance as slave on one board.

Master uses edma and slave uses edma way.

Please make sure you make the correct line connection. Basically, the connection is:

FLEXIO_SPI_master -- LPSPI_slave

CLK

CLK

--

PCS

PCS

SOUT

--

SIN

SIN

SOUT

This is LPSPI slave call back.

Master receives:

FE FD FC FB

FΑ

F9

F8

F6

F5

F4

F3

F2

F1

F0

ਸਸ

EF

EE ED EC EB

E8

Ε6

E1

ΕO

Slave transmits:

FC

F5

F3

FD

FB

F9

F8

F7

F6

F4

F2

F1

F0

FF

FE

FA

ED EC EB

E9

E7

EΑ

FLEXIO SPI master <-> LPSPI slave transfer all data matched!

End of example.

```

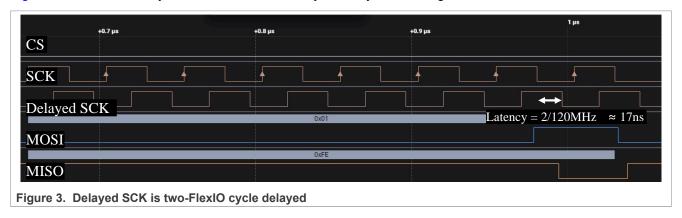

Figure 3 shows that Delayed SCK is a two-FlexIO cycle delayed as configured.

#### 4 Conclusion

By using additional timers, even timing parameters can be customized in the FlexIO emulated interface.

**Timing Parameter Tuning for FlexIO Emulated Interface**

#### 5 Note about the source code in the document

Example code shown in this document has the following copyright and BSD-3-Clause license:

Copyright 2024 NXP Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- 1. Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- 2. Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

- 3. Neither the name of the copyright holder nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

# 6 Revision history

Table 3 summarizes the revisions to this document.

Table 3. Revision history

| Document ID | Release date  | Description            |

|-------------|---------------|------------------------|

| AN14284 v.1 | 12 April 2024 | Initial public release |

#### **Timing Parameter Tuning for FlexIO Emulated Interface**

# Legal information

#### **Definitions**

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this document expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <a href="mailto:PSIRT@nxp.com">PSIRT@nxp.com</a>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

**NXP B.V.** — NXP B.V. is not an operating company and it does not distribute or sell products.

#### **Trademarks**

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

Kinetis - is a trademark of NXP B.V.

MCX — is a trademark of NXP B.V.

AN14284

# Timing Parameter Tuning for FlexIO Emulated Interface

#### **Contents**

| 1   | Introduction                        | 2 |

|-----|-------------------------------------|---|

| 2   | Emulation of SPI master             |   |

| 2.1 | Overview                            |   |

| 2.2 | Receiving error at a high baud rate | 2 |

| 3   | Setup time tuning by delayed clock  |   |

| 3.1 | What is a delayed clock             |   |

| 3.2 | Configuring the shifters and timers |   |

| 3.3 | Running the demo                    |   |

| 4   | Conclusion                          | 5 |

| 5   | Note about the source code in the   |   |

|     | document                            | 6 |

| 6   | Revision history                    |   |

| -   | Legal information                   |   |

|     |                                     |   |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.